# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出願年月日 Date of Application:

2002年10月28日

出 願 番 号 Application Number:

特願2002-313528

[ST. 10/C]:

[ J P 2 0 0 2 - 3 1 3 5 2 8 ]

出 願 人

Applicant(s):

シャープ株式会社

特許庁長官

Commissioner, Japan Patent Office 2003年 8月 4日

【書類名】

特許願

【整理番号】

02J02802

【提出日】

平成14年10月28日

【あて先】

特許庁長官 殿

【国際特許分類】

H01L 25/00

【発明者】

【住所又は居所】

大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】

木村 敏夫

【発明者】

【住所又は居所】

大阪府大阪市阿倍野区長池町22番22号 シャープ株

式会社内

【氏名】

土津田 義久

【特許出願人】

【識別番号】

000005049

【氏名又は名称】 シャープ株式会社

【代理人】

【識別番号】

100080034

【弁理士】

【氏名又は名称】

原 謙三

【電話番号】

06-6351-4384

【選任した代理人】

【識別番号】

100113701

【弁理士】

【氏名又は名称】 木島 隆一

【選任した代理人】

【識別番号】

100115026

【弁理士】

【氏名又は名称】 圓谷 徹

【選任した代理人】

【識別番号】

100116241

【弁理士】

【氏名又は名称】 金子 一郎

【手数料の表示】

【予納台帳番号】 003229

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】 0208489

【プルーフの要否】 要

## 【書類名】 明細書

【発明の名称】 積層型半導体装置及びその製造方法

## 【特許請求の範囲】

# 【請求項1】

素子領域から導かれる電極パッドの領域内に半導体チップの表裏間を貫通する 貫通電極が複数個接続されてなる半導体装置が複数積層されていることを特徴と する積層型半導体装置。

## 【請求項2】

前記各電極パッドは、素子領域を取り囲むように各半導体チップの周辺に設け られていることを特徴とすると請求項1記載の積層型半導体装置。

## 【請求項3】

前記貫通電極のうち少なくとも1種類は、前記電極パッドと電気的に接続される接続用貫通電極であることを特徴とする請求項1又は2記載の半導体装置。

## 【請求項4】

前記貫通電極のうち少なくとも1種類は、前記電極パッドとは電気的に接続されないスルー用貫通電極であることを特徴とする請求項1、2又は3記載の半導体装置。

#### 【請求項5】

前記電極パッドの領域外にさらに貫通電極が設けられていることを特徴とする 請求項1~4のいずれか1項に記載の積層型半導体装置。

### 【請求項6】

前記各半導体装置の貫通電極同士がバンプを介して接続されることにより、各 半導体装置が積層されていることを特徴とすると 1~5のいずれか1項に記載の 積層型半導体装置。

#### 【請求項7】

半導体装置を形成する半導体装置製造工程と、

上記半導体装置を複数積層する半導体装置積層工程とを含む一方、

上記半導体装置製造工程は、

素子領域から導かれた電極パッドの領域内に所定形状の開口部を有するマスク

を用いて、上記電極パッドを貫いて半導体チップに所定の深さを有する溝部を形成する工程と、

上記溝部の内壁に絶縁膜を形成する工程と、

上記溝部に導電材料を充填する工程と、

上記半導体チップの裏面の一部を除去して上記導電材料を露出させることにより、半導体チップの表裏を貫通する上記導電材料からなる貫通電極を形成する工程とをこの順に含むことを特徴とする積層型半導体装置の製造方法。

## 【請求項8】

前記半導体装置製造工程における溝部の内壁に絶縁膜を形成する工程と前記溝部に導電材料を充填する工程との間に、上記溝部の内壁に形成した絶縁膜のうち、電極パッドと同層部分を除去する工程を含むことを特徴とする請求項7記載の積層型半導体装置の製造方法。

## 【請求項9】

前記半導体装置製造工程において、前記電極パッドの領域外にもさらに貫通電極を形成する工程を含むことを特徴とする請求項7又は8記載の積層型半導体装置の製造方法。

### 【請求項10】

前記半導体装置製造工程において、前記溝部を形成する工程の前に、素子領域 から導かれる電極パッドを形成する工程を含むとともに、

上記電極パッドを形成する工程では、電極パッドの領域をマスク変更により省 スペース化して形成する一方、

上記省スペース化による電極パッド空き領域に貫通電極を形成する工程をさら に含むことを特徴とする請求項7又は8記載の積層型半導体装置の製造方法。

# 【請求項11】

前記半導体装置製造工程における電極パッドを貫いて半導体チップに所定の深 さを有する溝部を形成する工程において、上記溝部は電極パッドの領域内に複数 形成されることを特徴とする請求項7又は8記載の積層型半導体装置の製造方法

## 【発明の詳細な説明】

## $[0\ 0\ 0\ 1]$

# 【発明の属する技術分野】

本発明は、貫通電極を有する半導体装置、及びこの半導体装置を複数個積層することにより、高機能化、小型化及び薄型化を図るための積層型半導体装置及び その製造方法に関するものである。

# [0002]

# 【従来の技術】

近年、電子機器の小型化の要求に対応するものとして、また、組立工程の自動化に適合するものとして、CSP (Chip Size Package)型半導体装置が広く用いられている。

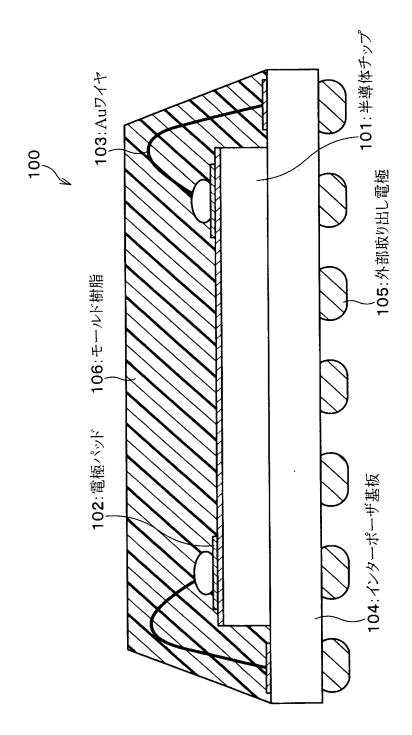

## [0003]

図30は、ワイヤボンドタイプのCSP型半導体装置100の断面構造の一例を示している。上記ワイヤボンドタイプのCSP型半導体装置100では、半導体チップ101の周辺に設けられた電極パッド102からAuワイヤ103を介して回路基板であるインターポーザ基板104に電気的な接続が行われ、インターポーザ基板104の裏面に設けられた外部取り出し電極105を介して、図示しない外部機器に接続されるようになっている。

#### $[0\ 0\ 0\ 4\ ]$

Auワイヤ103によるワイヤボンディングによって、半導体チップ101に 形成されている電極パッド102とインターポーザ基板104との電気的な接続 が行われる。このため、Auワイヤ103の高さ分だけ高くなり、さらにAuワイヤ103の保護のためにモールド樹脂106による封止が必要となるため、ワイヤボンドタイプのCSP型半導体装置100の薄型化が図り難いという問題点 を有している。

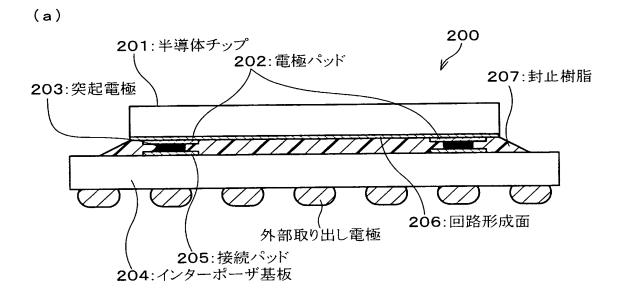

## [0005]

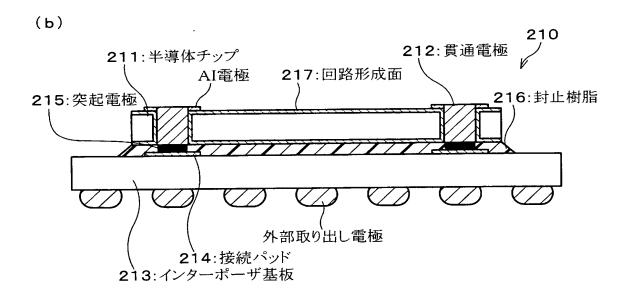

また、この問題を解決するために、図31(a)に示すFCB(Flip Chip Bonding)タイプのものと、図31(b)に示す貫通電極を有するもの等がある。これらのCSP型半導体装置では、ワイヤを不要とすることによって半導体装置の薄型化を図ることができる。

# [0006]

図31(a)に示すFCBタイプの半導体装置200では、半導体チップ201は、電極パッド202上に形成された突起電極203を介して、インターポーザ基板204の接続パッド205と電気的に接続されている。この時、半導体チップ201の回路形成面206とインターポーザ基板204とは対向する向きに接続され、回路形成面206とインターポーザ基板204との間には、半導体チップ201の保護と接続部の保護とのために封止樹脂207にて封止されている

## [0007]

また、図31(b)に示す貫通電極により電気的接続が行われた半導体装置210では、半導体チップ211に形成された貫通電極212とインターポーザ基板213に形成された接続パッド214とは、突起電極215を介して電気的に接続されている。必要に応じて、半導体チップ211とインターポーザ基板213との界面に、封止樹脂216を注入し封止することも可能である。この場合、半導体チップ211の回路形成面217は上向きである。

# [0008]

最近では、これらの半導体装置において、例えば特許文献1~特許文献3に開示されているように、実装効率を高めるために、半導体装置としてのフィルムキャリア半導体モジュールを複数積み重ねて、電気的に接続したマルチチップ半導体装置が提案されている。

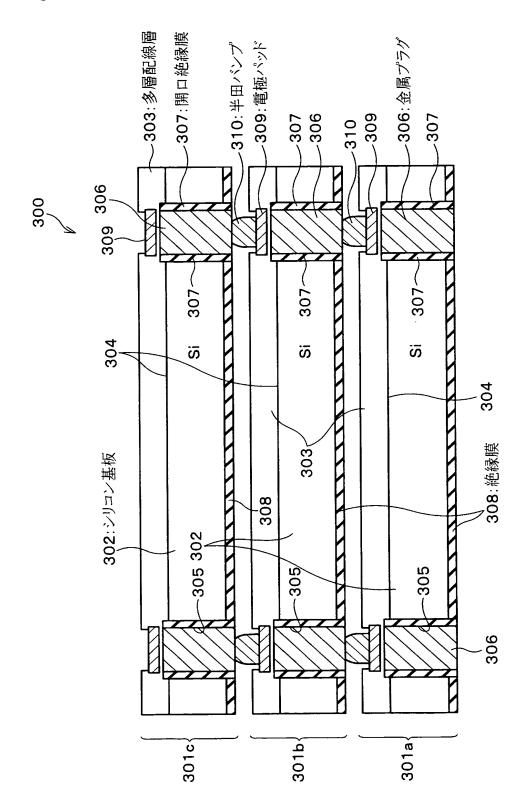

## [0009]

上記の特許文献1に記載のマルチチップ半導体装置300は、図32に示すように、3つの半導体装置301a・301b・301cが下から順に積層されてなっている。各半導体装置301a・301b・301cは、それぞれ、大きく分けて、素子がそれぞれ集積形成されたシリコン基板302・302・302と、集積形成された素子を所定の関係に接続するための多層配線層303・303・303と、これら各多層配線層303の層間絶縁膜304及び各シリコン基板302を貫通する貫通口305内に形成され、各半導体装置301a・301b及び半導体装置301b・301c同士を電気的に接続するための接続プラグで

ある貫通電極306及び開口絶縁膜307とから構成されている。上記貫通電極306…は、グランド端子や電源端子、及びその他の信号端子等の外部接続用端子に利用されるものであり、各半導体装置301a・301b・301c毎に、各用途に応じて複数設けられている。また、各シリコン基板302の裏面における上記貫通電極306以外の領域は裏面絶縁膜308にて被覆されている。

# [0010]

また、各半導体装置301a・301b・301cの各多層配線層303には、上記金属プラグ306に電気的に接続された電極パッド309がそれぞれ設けられている。そして、半導体装置301aの貫通電極306は、電極パッド309及び半田バンプ310を介して半導体装置301bの貫通電極306に接続されるとともに、半導体装置301bの貫通電極306は、電極パッド309及び半田バンプ310を介して半導体装置301cの貫通電極306に接続されている。

# $[0\ 0\ 1\ 1]$

これにより、各半導体装置301a・301b・301cは、相互に電気的に接続されていることになり、積層型半導体装置が完成される。

#### $[0\ 0\ 1\ 2]$

ところで、上記従来の積層型半導体装置では、上下間の電気的導通をとる場合 、同一信号端子は同じ端子位置にて上下間の電気的導通を確保している。

## [0013]

## 【特許文献1】

特開平10-223833号公報(1998年8月21日公開)

## [0014]

## 【特許文献2】

特許第3186941号公報(2001年5月11日発行)

## [0015]

### 【特許文献3】

US特許第6.184.060号明細書(2001年2月6日登録)

# [0016]

# 【発明が解決しようとする課題】

しかしながら、上記従来の貫通電極を形成した積層型半導体装置では、素子領域の外側に貫通孔を作成していたが、積層する半導体装置が多段になればなる程、貫通電極のための貫通孔が増加する。また、多段になる程、半導体装置は電気的な動作をせず、下層又は上層の半導体装置の橋渡し的な役目のみを行うスルー用貫通電極も必要になる。

# [0017]

この結果、貫通孔を形成するために積層型半導体装置の周辺部が大きくなり、 積層型半導体装置の小型化が図れないという問題点を有している。

## [0018]

本発明は、上記従来の問題点に鑑みなされたものであって、その目的は、多数の貫通電極を設けることに伴う、装置の大型化防止及び多段積層の困難化解消を図り得る積層型半導体装置及びその製造方法を提供することにある。

## [0019]

# 【課題を解決するための手段】

本発明の積層型半導体装置は、上記課題を解決するために、素子領域から導かれる電極パッドの領域内に半導体チップの表裏間を貫通する貫通電極が複数個接続されてなる半導体装置が複数積層されていることを特徴としている。

# [0020]

すなわち、従来では、貫通電極を電極パッドの領域外における電極パッドの周 辺に設け、その貫通電極を介して上下の半導体装置のコンタクトを取っていた。

#### [0021]

しかし、この場合、半導体装置の積層数が増加すると貫通電極の本数が増え、 半導体チップの周辺に広い貫通電極のスペースを設けなければならないので、積 層型半導体装置の小型化が図れないという問題があった。

#### [0022]

しかし、本発明では、電極パッドの領域内に半導体チップの表裏間を貫通する 貫通電極が複数個接続されてなる。したがって、電極パッドの領域を貫通電極の 形成スペースに使用できる。

# [0023]

この結果、半導体チップの周辺部を広く形成する必要がないので、半導体チップの周辺部だけではスペースを確保できなくなるのを緩和させることができるとともに、積層型半導体装置の小型化を図ることができる。また、多段積層も容易に実現できるようになる。

## [0024]

したがって、多数の貫通電極を設けることに伴う、装置の大型化防止及び多段 積層の困難化解消を図り得る積層型半導体装置を提供することができる。

## [0025]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記各電極パッドは、素子領域を取り囲むように各半導体チップの周辺に設けら れていることを特徴としている。

# [0026]

上記の発明によれば、前記各電極パッドは、素子領域を取り囲むように各半導体チップの周辺に設けられているので、貫通電極を形成する際に素子領域が邪魔になるということがない。

#### [0027]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記貫通電極のうち少なくとも1種類は、前記電極パッドと電気的に接続される 接続用貫通電極であることを特徴としている。

## [0028]

上記の発明によれば、貫通電極のうち少なくとも1種類は、前記電極パッドと 電気的に接続される接続用貫通電極である。

# [0029]

このため、一般的な素子領域に接続される接続用貫通電極を形成することができる。

#### [0030]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記貫通電極のうち少なくとも1種類は、前記電極パッドとは電気的に接続され ないスルー用貫通電極であることを特徴としている。

# [0031]

上記の発明によれば、貫通電極のうち少なくとも1種類は、前記電極パッドとは電気的に接続されないスルー用貫通電極である。したがって、貫通電極として、素子領域に接続されないで単に半導体装置をスルーするためだけのスルー用貫通電極が設けられることになる。この結果、半導体装置に発生する熱をスルー用貫通電極を介して外部に逃したり、上層の半導体装置の接続用貫通電極に連結することにより、下層の半導体装置側に導くことができる。

## [0032]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記電極パッドの領域外にさらに貫通電極が設けられていることを特徴としてい る。

# [0033]

上記の発明によれば、電極パッドの領域外にさらに貫通電極が設けられているので、電極パッドの領域内に貫通電極を形成し、さらに、電極パッドの領域外にもさらに貫通電極を形成することによって、多層の積層型半導体装置にも対応することが可能となる。

#### [0034]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記各半導体装置の貫通電極同士がバンプを介して接続されることにより、各半 導体装置が積層されていることを特徴としている。

#### [0035]

上記の発明によれば、各半導体装置の貫通電極同士がバンプを介して接続されることにより、各半導体装置が積層されているので、積層工程を容易に行うことができる。

# [0036]

また、本発明の積層型半導体装置の製造方法は、上記課題を解決するために、 半導体装置を形成する半導体装置製造工程と、上記半導体装置を複数積層する半 導体装置積層工程とを含む一方、上記半導体装置製造工程は、素子領域から導か れた電極パッドの領域内に所定形状の開口部を有するマスクを用いて、上記電極 パッドを貫いて半導体チップに所定の深さを有する溝部を形成する工程と、上記 溝部の内壁に絶縁膜を形成する工程と、上記溝部に導電材料を充填する工程と、 上記半導体チップの裏面の一部を除去して上記導電材料を露出させることにより 、半導体チップの表裏を貫通する上記導電材料からなる貫通電極を形成する工程 とをこの順に含むことを特徴としている。

# [0037]

上記の発明によれば、積層型半導体装置の製造方法は、まず、半導体装置を形 成する半導体装置製造工程と、上記半導体装置を複数積層する半導体装置積層工 程とを含む。

## [0038]

そして、上記半導体装置製造工程は、素子領域から導かれた電極パッドの領域 内に所定形状の開口部を有するマスクを用いて、上記電極パッドを貫いて半導体 チップに所定の深さを有する溝部を形成する工程と、上記溝部の内壁に絶縁膜を 形成する工程と、上記溝部に導電材料を充填する工程と、上記半導体チップの裏 面の一部を除去して上記導電材料を露出させることにより、半導体チップの表裏 を貫通する上記導電材料からなる貫通電極を形成する工程とをこの順に含む。

# [0039]

したがって、この工程にて積層型半導体装置を製造することにより、例えば、 既存の電極パッドが形成された半導体装置にて積層型半導体装置の製造する場合 において、容易に、電極パッドの領域内に貫通電極を形成することができる。

#### $[0\ 0\ 4\ 0\ ]$

したがって、多数の貫通電極を設けることに伴う、装置の大型化防止及び多段 積層の困難化解消を図り得る積層型半導体装置の製造方法を提供することができ る。

#### [0041]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置 の製造方法において、前記半導体装置製造工程における溝部の内壁に絶縁膜を形 成する工程と前記溝部に導電材料を充填する工程との間に、上記溝部の内壁に形 成した絶縁膜のうち、電極パッドと同層部分を除去する工程を含むことを特徴と している。

# [0042]

上記の発明によれば、前記半導体装置製造工程における溝部の内壁に絶縁膜を 形成する工程と前記溝部に導電材料を充填する工程との間に、上記溝部の内壁に 形成した絶縁膜のうち、電極パッドと同層部分を除去する工程を含む。

# [0043]

したがって、これにより、スルー用貫通電極を容易に形成することができる。

# [0044]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置の製造方法において、前記半導体装置製造工程において、前記電極パッドの領域外にもさらに貫通電極を形成する工程を含むことを特徴としている。

## [0045]

上記の発明によれば、前記半導体装置製造工程において、前記電極パッドの領域外にもさらに貫通電極を形成する工程を含む。したがって、電極パッドの領域内に貫通電極1を形成し、さらに、電極パッドの領域外にもさらに貫通電極を形成することによって、多層の積層型半導体装置にも対応できる積層型半導体装置を容易に製造することができる。

## [0046]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置の製造方法において、前記半導体装置製造工程において、前記溝部を形成する工程の前に、素子領域から導かれる電極パッドを形成する工程を含むとともに、上記電極パッドを形成する工程では、電極パッドの領域をマスク変更により省スペース化して形成する一方、上記省スペース化による電極パッド空き領域に貫通電極を形成する工程をさらに含むことを特徴としている。

### [0047]

上記の発明によれば、前記半導体装置製造工程において、前記溝部を形成する 工程の前に、素子領域から導かれる電極パッドを形成する工程を含むとともに、 上記電極パッドを形成する工程では、電極パッドの領域をマスク変更により省ス ペース化して形成する一方、上記省スペース化による電極パッド空き領域に貫通 電極を形成する工程をさらに含む。

# [0048]

したがって、従来では、大きな電極パッドが存在したが、その電極パッドを小さく形成することによって、従来電極パッドがあるはずの箇所に生まれたスペースにさらに貫通電極を形成することができる。

## [0049]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置の製造方法において、前記半導体装置製造工程における電極パッドを貫いて半導体チップに所定の深さを有する溝部を形成する工程において、上記溝部は電極パッドの領域内に複数形成されることを特徴としている。

## [0050]

上記の発明によれば、前記半導体装置製造工程における電極パッドを貫いて半 導体チップに所定の深さを有する溝部を形成する工程において、上記溝部は電極 パッドの領域内に複数形成される。

## [0051]

このため、一つの電極パッドの領域内に、接続用貫通電極とスルー用貫通電極 とを複数個形成することができる。

# [0052]

## 【発明の実施の形態】

#### 「実施の形態1〕

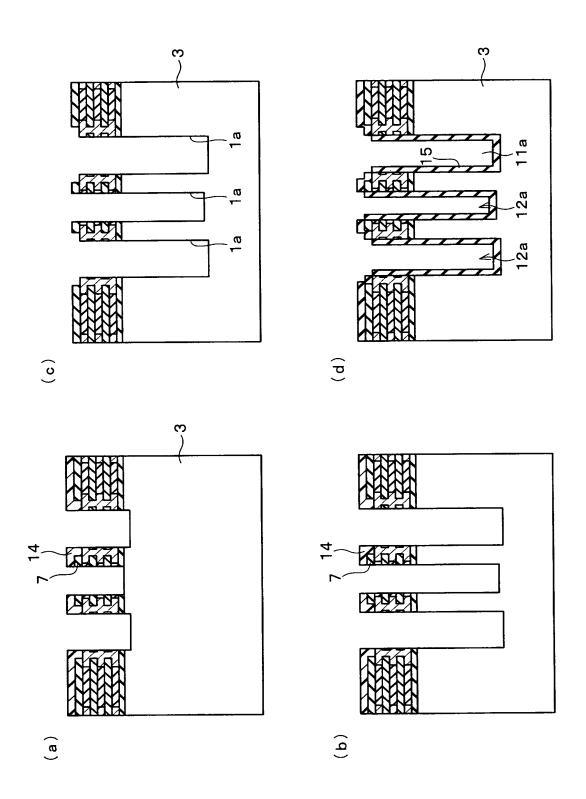

本発明の実施の一形態について図1ないし図9に基づいて説明すれば、以下の 通りである。

## [0053]

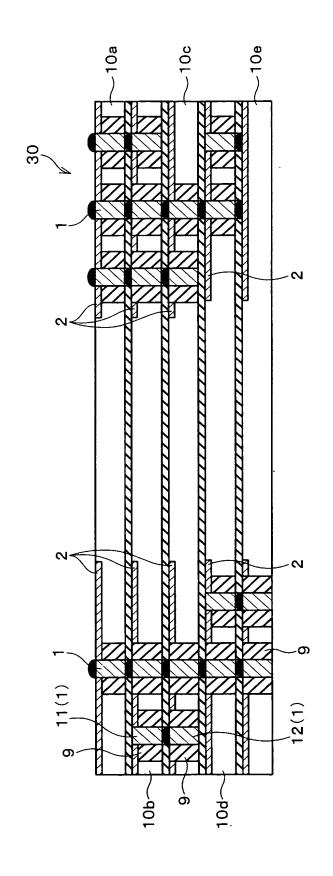

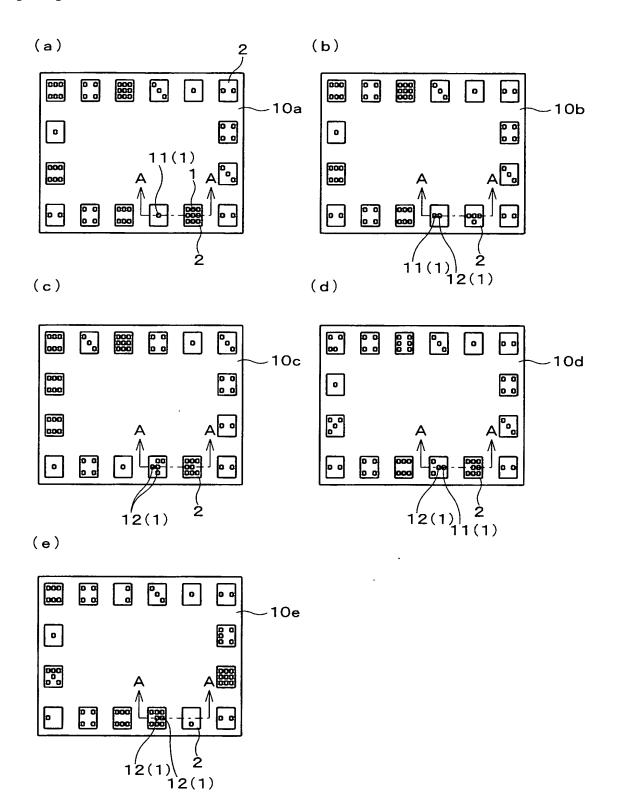

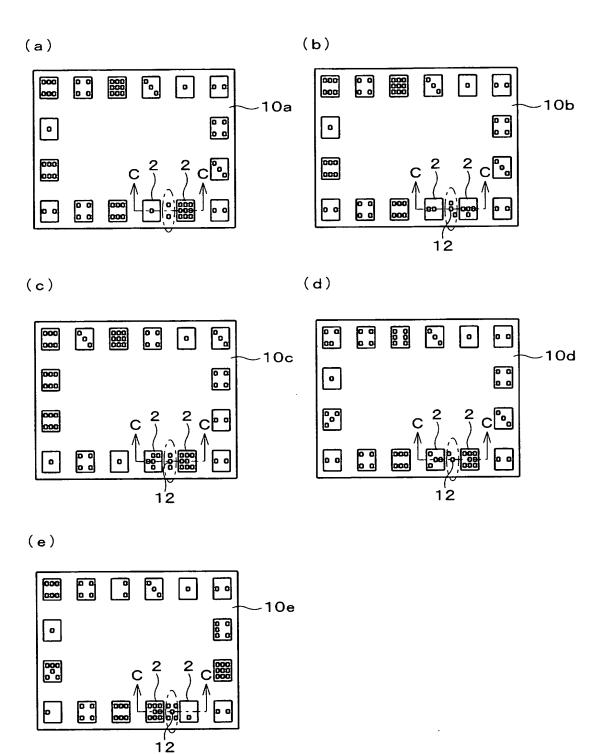

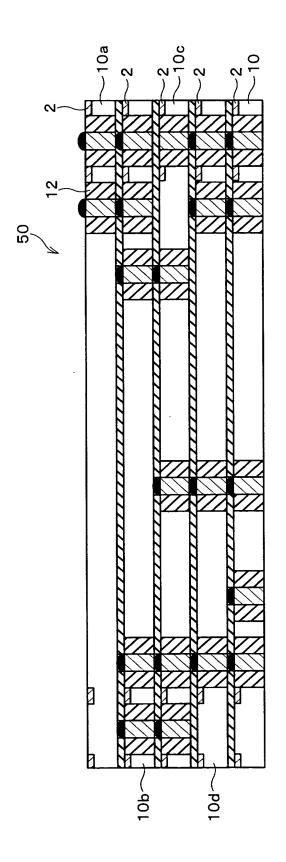

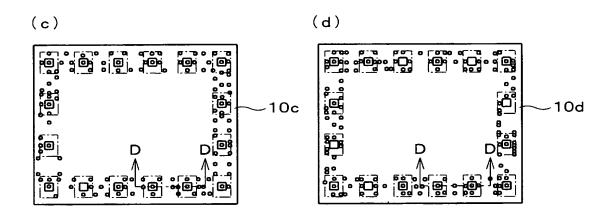

本実施の形態の積層型半導体装置30は、図1に示すように、上側から順に第1半導体装置10a、第2半導体装置10b、第3半導体装置10c、第4半導体装置10d、及び第5半導体装置10eの例えば5段の各半導体装置10が積層されたものからなっている。なお、本実施の形態では、5段の各半導体装置10が積層されたものからなっているが、必ずしもこれに限らず、他の複数段であ

ってもよい。

# [0054]

上記の積層型半導体装置30には、各半導体装置10…を相互に電気的に接続するために、1個の半導体装置10における後述する半導体チップ8の表裏間を貫通する貫通電極1…が設けられている。これによって、例えば、最上段の第1半導体装置10aの表面に形成された電極パッド2が、最下段の第5半導体装置10eの裏面から外部の図示しない例えばインターポーザ基板等の基板に接続可能となっている。

## [0055]

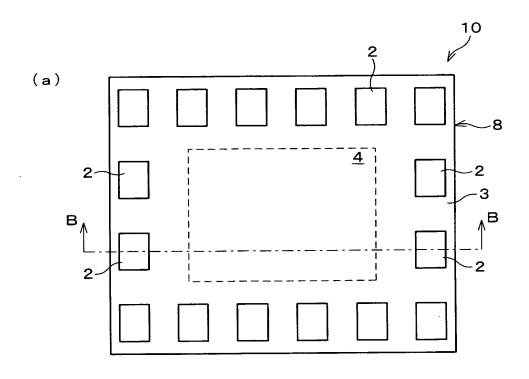

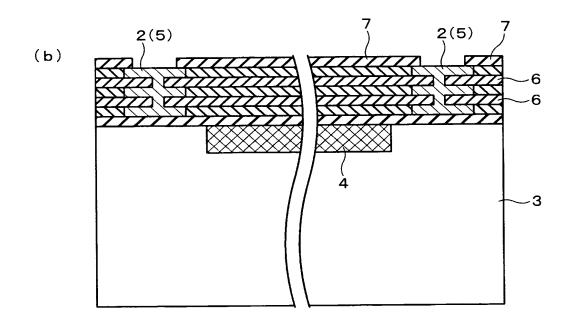

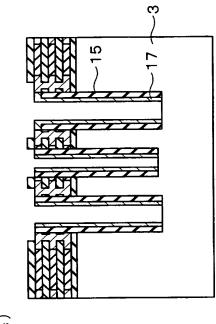

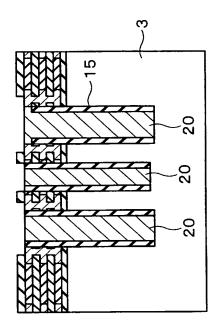

すなわち、各半導体装置10における半導体チップ8の基本形態は、図3(a)(b)に示すように、半導体ウエハからなるシリコン(Si)基板3の略中央位置に素子領域4を有し、その素子領域4からは複数の3層になったアルミニウム(A1)又は銅(Cu)からなる図示しない配線パターンが互いに層間絶縁膜6…にて絶縁された状態で外側に延びて形成されている。

## [0056]

上記各配線パターンの先端は、半導体チップ8の周辺部に設けられた電極パッド2まで延びており、この電極パッド2は半導体チップ8の表面に形成されているパッシベーション膜7から露出したものとなっている。上記電極パッド2…は、半導体チップ8の周辺部において、素子領域4を取り囲むように複数設けられており、これら電極パッド2…は、外部取り出し用電極の機能を果たすものとなっている。なお、本実施の形態では、3層の配線パターンについて説明しているが、配線パターンは必ずしも3層に限らず、1層でもよく、又は他の複数でも良い。

## [0057]

すなわち、半導体チップ8内には、素子領域4から延びる無数の微細な配線が 配線パターンとして走っている。上記の電極パッド2は、上記の配線パターンの 中で外部との電気的なやり取りを行うために、配線パターンの先端に設けられか つ半導体チップ8の周辺に配置されている比較的大きな電極端子をいうものであ り、半導体チップ8の表面に露出するものである。

## [0058]

また、上記の素子領域4は、半導体素子の電気的な動きのある場所をいうものであり。スイッチングを行う部分をいう。具体的には、ソース・ゲート・ドレインの部分である。

# [0059]

本実施の形態の積層型半導体装置30は、上記基本形態の構成を有する半導体 装置10を5段に積層したものである。

## [0060]

ところで、積層型半導体装置30において各半導体装置10…を積層するためには、貫通電極1の形成が必要となる。ここで、従来では、上記電極パッド2の外側に貫通孔を形成して貫通電極1を作成していたが、積層する半導体装置10…が多段になればなる程貫通電極1のための貫通孔が増加する。また、多段になる程、下層又は上層の半導体装置10の橋渡し的な役目のみを行うスルー用貫通電極も必要になる。すなわち、例えば、3段積層の半導体装置と5段積層の半導体装置とでは、行って帰る信号の箇所が同じとは限らず、違う箇所に信号が帰ることもあるので、貫通電極1の数は増える。

## $[0\ 0\ 6\ 1]$

この結果、貫通孔を形成するために半導体チップ8の周辺部が大きくなり、積 層型半導体装置の小型化が図り難いという問題点があった。

## [0062]

そこで、本実施の形態では、図1及び図2 (a) ~ (e) に示すように、上記の電極パッド2の領域内に貫通電極1を形成するようにしている。

## [0063]

この積層型半導体装置30では、図1において最も左には、第2半導体装置10bと第3半導体装置10cとの接続を図るために第2半導体装置10bの電極パッド2に接続される貫通電極1となっているとともに、第3半導体装置10cの貫通電極1は絶縁膜9によって第3半導体装置10cの電極パッド2とは絶縁されたものとなっている。

# [0064]

ここで、本実施の形態では、電極パッド2に接続される貫通電極1を接続用貫通電極11と呼ぶ一方、電極パッド2に接続されない貫通電極1をスルー用貫通電極12と呼んでいる。

## [0065]

したがって、図1において左から2つ目の貫通電極1は、第1半導体装置10 aが接続用貫通電極11であり、第2半導体装置10b~第5半導体装置10e はスルー用貫通電極12…となっている。すなわち、スルー用貫通電極12は、 前述したように、下層又は上層の半導体装置10…の橋渡し的な役目のみを行っ ている。

#### [0066]

また、本実施の形態の積層型半導体装置30では、上側から2段目の第2半導体装置10bにおける同図1の左側の電極パッド2に着目すると、この電極パッド2は第2半導体装置10bにおける前記素子領域4からの一つの信号を取り出して下層の第3半導体装置10cに接続するためのものである一方、この電極パッド2の領域内に、図1において左から2つ目の貫通電極1であるスルー用貫通電極12が形成されているものとなっている。

#### [0067]

したがって、本実施の形態では、ある信号を流すための電極パッド2の領域内に、異なる信号を流すためのスルー用貫通電極12が形成されているということにもなる。

#### [0068]

本実施の形態では、図2(a)~(e)に示すように、この電極パッド2内の領域には、例えば、 $1\sim9$ 個の貫通電極1を形成している。ただし、必ずしもこれに限らず、さらに多くの貫通電極1…を形成することが可能である。このように、本実施の形態の積層型半導体装置 30では、電極パッド2の領域内に、貫通電極1…が複数形成されている。そして、その電極パッド2の領域内の貫通電極1は、接続用貫通電極11又はスルー用貫通電極12のいずれであってもよい。

### [0069]

なお、本実施の形態では、当初の各半導体装置10は、電極パッド2の下に未 だ貫通電極1が形成されていない半導体装置であることを前提に説明しているが 、必ずしもこれに限らず、既に電極パッド2の下に貫通電極1が存在する半導体 装置であってもよい。その電極パッド2の空き領域に追加の貫通電極1を形成す ることができるためである。

# [0070]

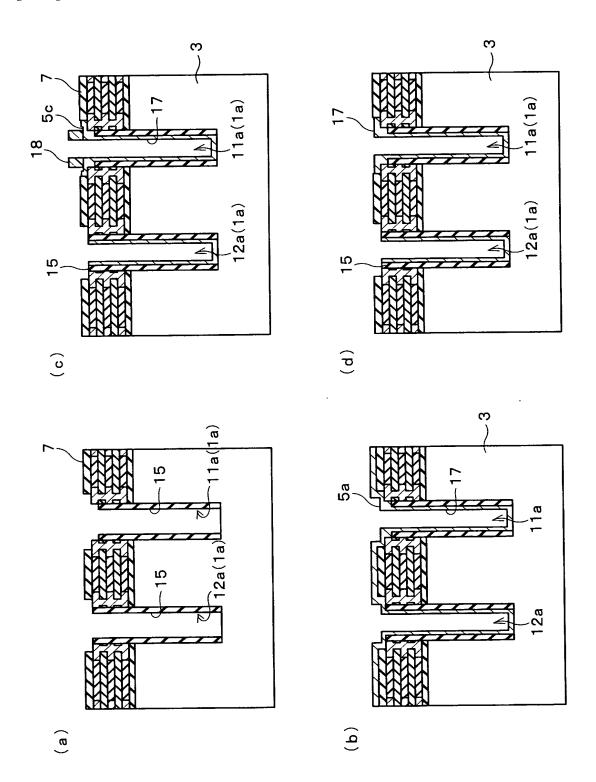

上記構成の半導体装置10における電極パッド2に、接続用貫通電極11とスルー用貫通電極12との貫通電極1を同時に形成する方法について図4~図10に基いて説明する。

## [0071]

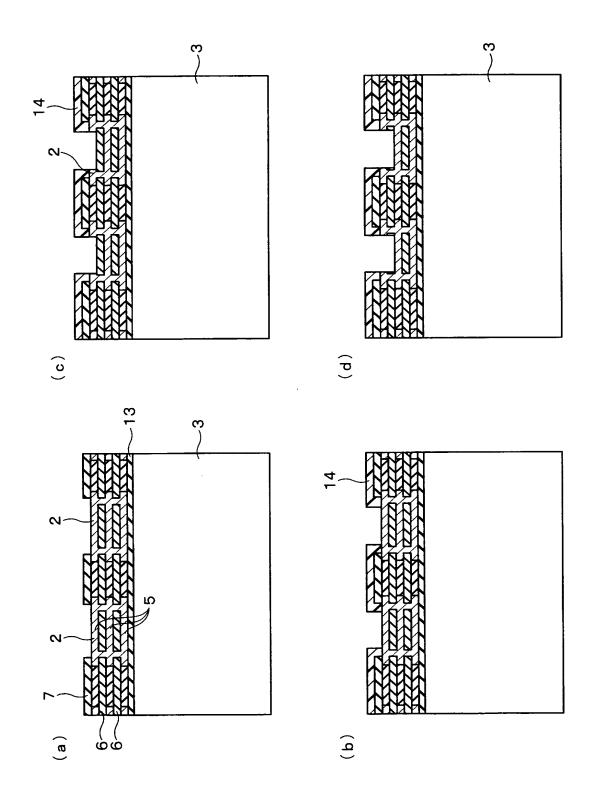

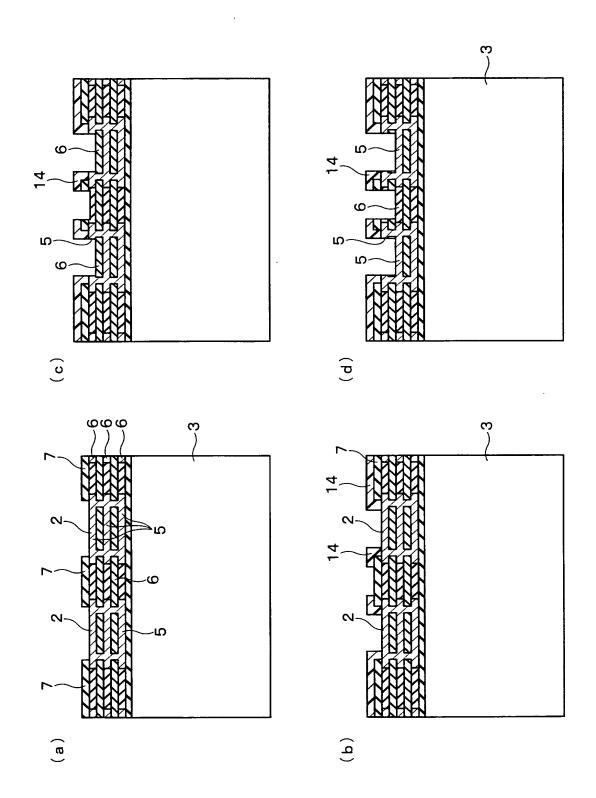

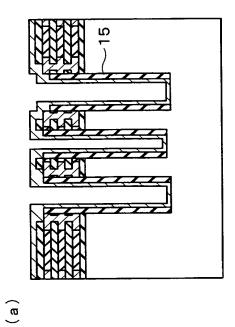

例えば、図4 (a)に示すように、半導体装置10の周辺部において、表面のパッシベーション膜7から露出する電極パッド2が2箇所に設けられているとする。上記の電極パッド2の大きさは、例えば70μm角である。

## [0072]

これら電極パッド2…の下側には、2層の配線パターン5…が層間絶縁膜6・6を介して形成されている。すなわち、配線パターン5…は3層からなり、最上層の配線パターン5が電極パッド2となっている。また、最下層の配線パターン5の下側には、層間膜13が設けられており、その下側はシリコン(Si)基板3となっている。上記の配線パターン5は、例えば、金属配線にてなり、直接電気を流すための配線である。通常、アルミニウム(A1)99%にシリコン(Si)1%、アルミニウム(A1)99%に銅(Cu)1%、アルミニウム(A1)+パラジウム(Pd)、又は銅(Cu)のみ等の金属が用いられる。なお、本発明においては、この金属の種類にはこだわらない。

#### [0073]

この電極パッド2に貫通電極1を形成するための貫通孔作成の前準備として、まず、図4(b)に示すように、ウエハ全体にレジスト14の塗布を行う。次いで、貫通パターン作成のため、縮小投影型露光機を使用し、電極パッド2の領域内に例えば10μm角の貫通孔用のパターンを1カ所から最大9ヶ所を開口し、電極パッド2を露出した状態にする。なお、説明においては、分かり易くするた

ページ: 16/

め、各電極パッド2に1個の貫通孔を形成することとする。

# [0074]

ここで、上記縮小投影型露光機は、世間一般では「ステッパー」と呼ばれており、微細な加工を行い易くするための装置として、半導体製造には欠かせないものである。この縮小投影型露光機では、マスクを等倍では使用せず縮小することによって微細なパターニングができる。すなわち、等倍で有ればマスク作成時に $1 \mu m$ パターンは難しいが、1:5のステッパーであれば $5 \mu m$ の形状で作成できるようになる。

## [0075]

次いで、図4 (c)に示すように、ドライエッチングにて、露光した部分であるアルミニウム (A1) ーシリコン (Si)配線又はアルミニウム (A1) ー銅 (Cu)配線からなる電極パッド2のエッチングを行う。ここで、ドライエッチングとは、化学反応を利用して材料層や薄膜を形状加工するエッチング (蝕刻)のうち、ガスやプラズマやイオンにより気相-固相界面反応を用いる方法をいう。エッチング種が材料表面に吸着されると化学反応が起こり、表面から離脱した生成物を外部を廃棄除去することによってエッチングが進行する。薬液を使用するウエットエッチング (湿式蝕刻)に対し、乾式蝕刻とも呼ばれるものである。

# [0076]

次いで、腐食が発生しないように直ぐに防腐食処理を行う。具体的には、ポリマー除去→水洗処理を行う。続けて、図4 (d)に示すように、層間絶縁膜6をドライエッチングにてエッチングする。ここで、ドライエッチャーでは異種の膜質を連続エッチングするが、使用ガス種の違いからなるチャンバ内の雰囲気や、特に金属腐食等を懸念してできるだけ大気に触れない理由からも、マルチチャンバ型ドライエッチャーを使用するのが好ましい。

## [0077]

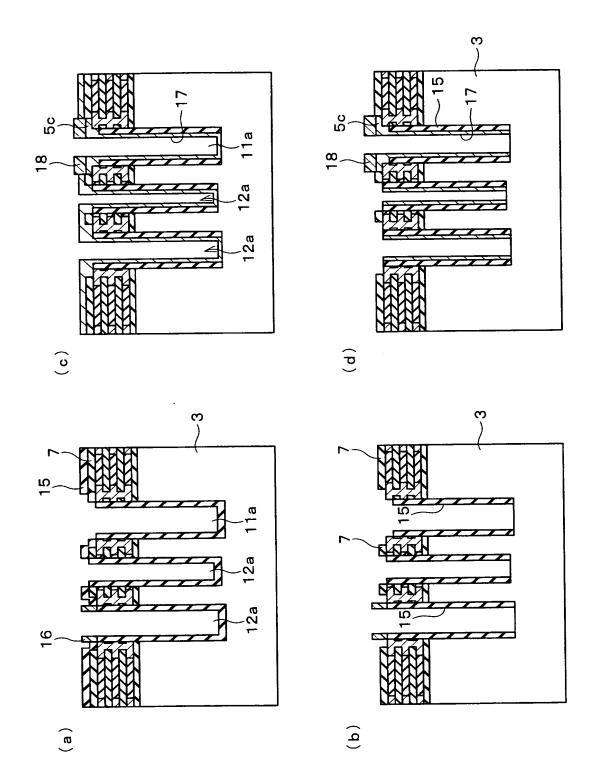

次いで、図5(a)(b)(c)(d)に示すように、上記の工程を、さらに 2層の配線パターン5・5について繰り返し、層間膜13をエッチングすること により、シリコン(Si) 基板3の上面にまで到達する。

### [0078]

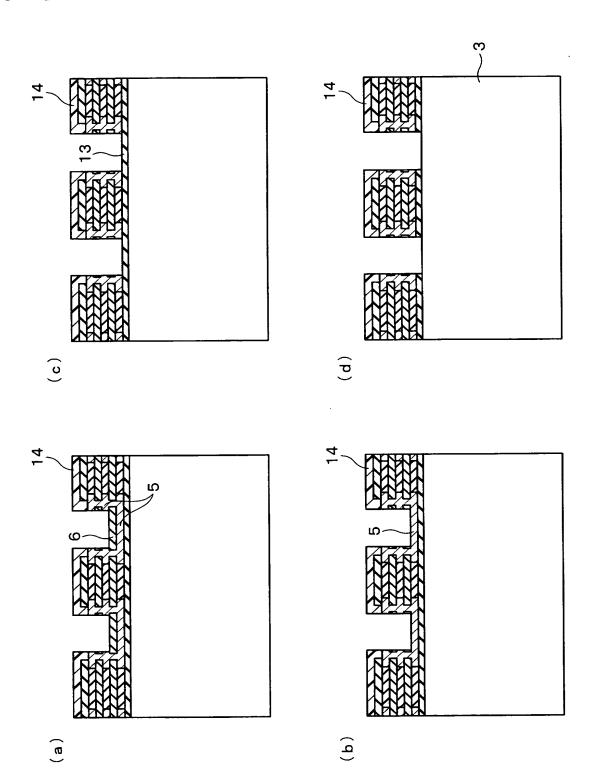

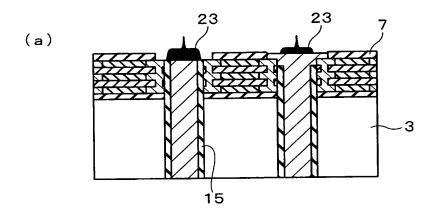

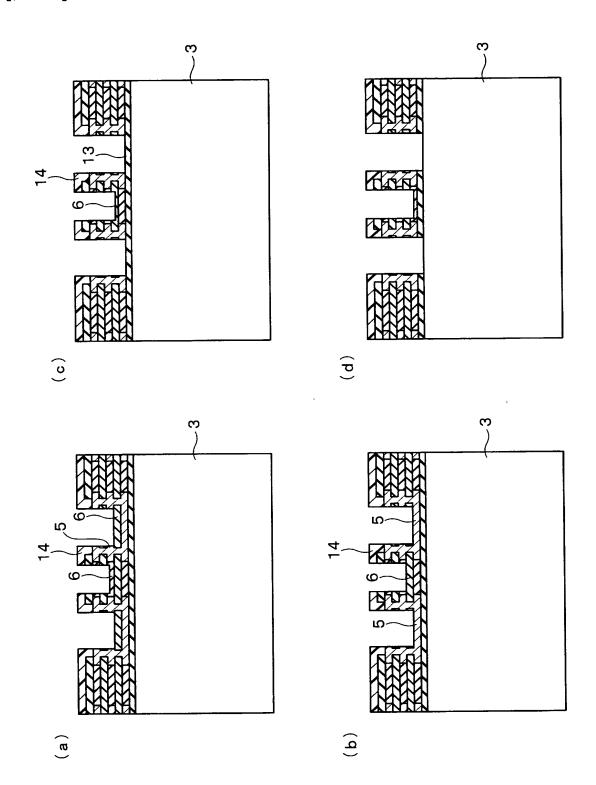

次いで、図 6 (a) に示すように、シリコン (S i) 深堀用ドライエッチャーにてシリコン (S i) 基板 3 のエッチングを行う。このときのシリコン (S i) 基板 3 のエッチングは、例えば 5 0  $\mu$  mから 7 0  $\mu$  mであり、シリコン (S i) 基板 3 の層厚さの途中で終了する。

# [0079]

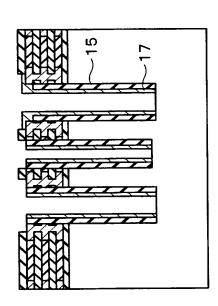

次いで、図6(b)に示すように、パッシベーション膜 7 の上面に塗布されていたレジスト 1 4 の剥離を行い、図6(c)に示すように、接続用貫通電極 1 1 のための貫通孔 1 a である接続用貫通電極貫通孔 1 1 a 及びスルー用貫通電極 1 2 のための貫通孔 1 a であるスルー用貫通電極貫通孔 1 2 a の壁面に絶縁膜成長設備にて側壁絶縁膜 1 5 を成長させる。本実施の形態では、深い穴の内壁に側壁絶縁膜 1 5 を形成するために、化学気相成長 (C V D:Chemical Vapor Deposition)によって T E O S (Tetra Etyl Ortho Silicate)酸化膜を形成した。今回は、内壁に例えば  $1 \mu$  m程度の厚みが形成されるようにした。なお、この T E O S 酸化膜とは、二酸化ケイ素(S i O 2)の化学気相成長(C V D)で用いられる液体ソースの一種である T E O S を使ってシリコン(S i)上に形成した酸化膜のことをいう。

# [0080]

上記の側壁絶縁膜15は、ウエハ表面にも成長するので、ドライエッチャーにてエッチバックを行い表面の側壁絶縁膜15を取り除く必要がある。このとき、スルー用貫通電極貫通孔12aの側壁表面部は側壁絶縁膜15を残しておきたいので、図6(d)に示すように、先に、レジスト16を塗布した後に、縮小投影型露光機にてパターニングしカバーする。その後、図7(a)に示すように、反応性イオンエッチング(RIE:Reactive Ion Etching)を用いて表面の側壁絶縁膜15をエッチングにて除去し、さらに、レジスト16を剥離する。なお、上記の反応性イオンエッチング(RIE)は、チャンバー(化学反応室)内のガスを電場や磁場でプラズマ化し、方向性を有する反応性イオン種を用いて行うエッチングである。化学反応と同時に進行するスパッタリング作用により、サイドエッチのない垂直断面形状が得易いため微細パターンの加工に適しているものである

# [0081]

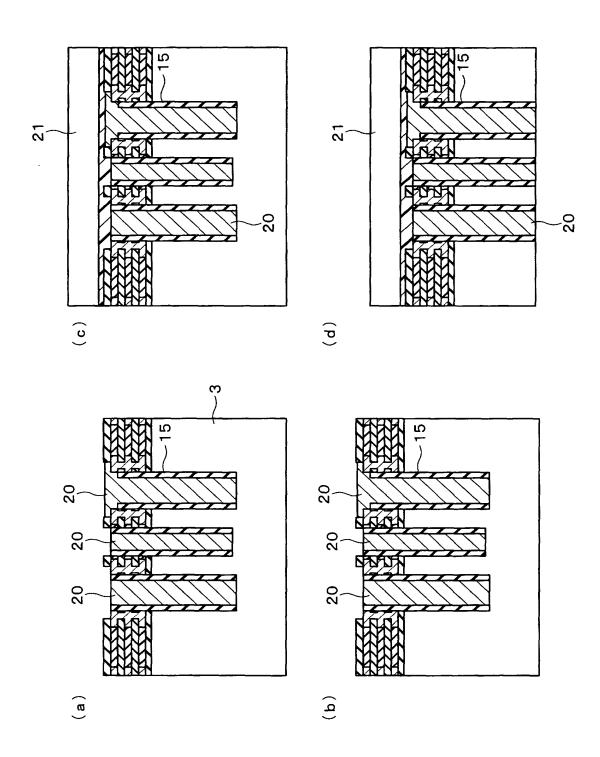

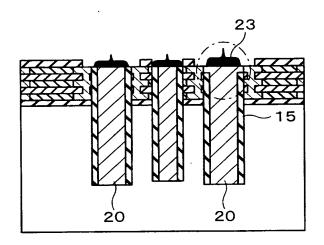

次いで、図7(b)に示すように、シード層である金属膜17をスパッタし、図7(c)に示すように、レジスト18を塗布することにより、必要な部分である接続用貫通電極貫通孔11aの内部及びスルー用貫通電極貫通孔12aの内部とウエハ上部の再配線パターン5aとを残してエッチングを行い、図7(d)に示すように、レジスト剥離後、図8(a)に示すように、無電解メッキ技術を使用して導体20を成長させる。

# [0082]

次いで、図8(b)に示すように、ウエハ表面に補強板21をUV接着シート22にて張り合わせ、図8(c)に示すように、シリコン(Si)基板3の裏面研磨を実施する。これにより、貫通電極1の裏面側が露出され、その後、図8(d)に示すように、補強板21を取り除く。

## [0083]

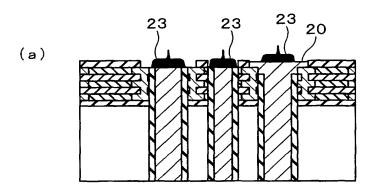

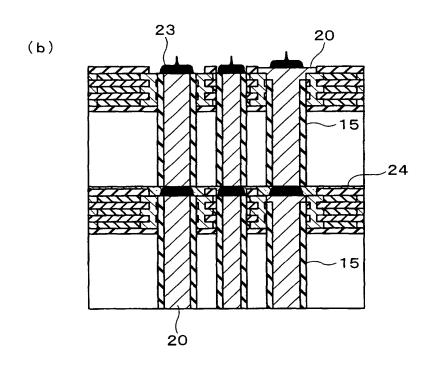

次いで、図9(a)に示すように、成長した導体20の上に例えば金ワイヤバンプからなるバンプ23を付け、図9(b)に示すように、導電性シート24にて上下の半導体装置10・10を密着させて完了する。

#### [0084]

なお、上記の例では、バンプ23として、金ワイヤバンプで作成を行っている。したがって、バンプ作成に際して、周りがアルミニウム(A1)ーシリコン(Si)又はアルミニウム(A1)ー銅(Cu)からなる導体20であるので、スルー用貫通電極貫通孔12aとなる箇所のバンプ作成は周りの導体20にショートしないように慎重に行う必要がある。

### [0085]

このように、本実施の形態の積層型半導体装置30では、電極パッド2の領域 内に半導体チップ8の表裏間を貫通する貫通電極1が複数個接続されてなる。し たがって、電極パッド2の領域を貫通電極1の形成スペースに使用できる。

#### [0086]

この結果、半導体チップ8の周辺部を広く形成する必要がないので、半導体チップ8の周辺部だけではスペースを確保できなくなるのを緩和させることができ

るとともに、積層型半導体装置30の小型化を図ることができる。また、多段積 層も容易に実現できるようになる。

## [0087]

したがって、多数の貫通電極1を設けることに伴う、装置の大型化防止及び多 段積層の困難化解消を図り得る積層型半導体装置30を提供することができる。

## [0088]

また、本実施の形態の積層型半導体装置30では、各電極パッド2は、素子領域4を取り囲むように各半導体チップ8の周辺に設けられているので、貫通電極1を形成する際に、素子領域4が邪魔になるということがない。

## [0089]

また、本実施の形態の積層型半導体装置30では、貫通電極1のうち少なくとも1種類は、電極パッド2と電気的に接続される接続用貫通電極11である。

## [0090]

このため、一般的な素子領域4に接続される接続用貫通電極11を形成することができる。

### [0091]

また、本実施の形態の積層型半導体装置30では、貫通電極1のうち少なくとも1種類は、電極パッド2とは電気的に接続されないスルー用貫通電極12である。したがって、貫通電極1として、素子領域4に接続されないで単に半導体装置10をスルーするためだけのスルー用貫通電極12が設けられることになる。この結果、半導体装置10に発生する熱をスルー用貫通電極12を介して外部に逃したり、上層の半導体装置10の接続用貫通電極11に連結することにより、下層の半導体装置10側に導くことができる。

#### [0092]

また、本実施の形態の積層型半導体装置30では、各半導体装置10の貫通電極1同士がバンプ23を介して接続されることにより、各半導体装置10が積層されているので、積層工程を容易に行うことができる。

#### [0093]

また、本実施の形態の積層型半導体装置30は、まず、半導体装置10を形成

する半導体装置製造工程と、上記半導体装置 10 を複数積層する半導体装置積層 工程とを含む。

# [0094]

そして、上記半導体装置製造工程は、素子領域4から導かれた電極パッド2の領域内に所定形状の開口部を有するマスクであるレジスト14を用いて、電極パッド2を貫いて半導体チップ8に所定の深さを有する溝部である貫通孔1aを形成する工程と、上記貫通孔1aの内壁に絶縁膜としての側壁絶縁膜15を形成する工程と、貫通孔1aに導電材料である導体20を充填する工程と、上記半導体チップ8の裏面の一部を除去して上記導電材料を露出させることにより、半導体チップ8の表裏を貫通する上記導電材料からなる貫通電極1を形成する工程とをこの順に含む。

# [0095]

したがって、この工程にて積層型半導体装置30を製造することにより、例えば、既存の電極パッド2が形成された半導体装置10にて積層型半導体装置30の製造する場合において、容易に、電極パッド2の領域内に貫通電極1を形成することができる。

#### [0096]

したがって、多数の貫通電極1を設けることに伴う、装置の大型化防止及び多 段積層の困難化解消を図り得る積層型半導体装置30の製造方法を提供すること ができる。

## [0097]

また、本実施の形態の積層型半導体装置30の製造方法は、半導体装置製造工程における貫通孔1aの内壁に側壁絶縁膜15を形成する工程と貫通孔1aに導電材料を充填する工程との間に、貫通孔1aの内壁に形成した側壁絶縁膜15のうち、電極パッド2と同層部分を除去する工程を含む。

## [0098]

したがって、これにより、スルー用貫通電極 1 2 を容易に形成することができる。

# [0099]

また、本実施の形態の積層型半導体装置30の製造方法は、半導体装置製造工程における電極パッド2を貫いて半導体チップ8に所定の深さを有する貫通孔1 aを形成する工程において、貫通孔1aは電極パッド2の領域内に複数形成される。

## $[0 \ 1 \ 0 \ 0]$

このため、一つの電極パッド2の領域内に、接続用貫通電極11とスルー用貫通電極12とを複数個形成することができる。

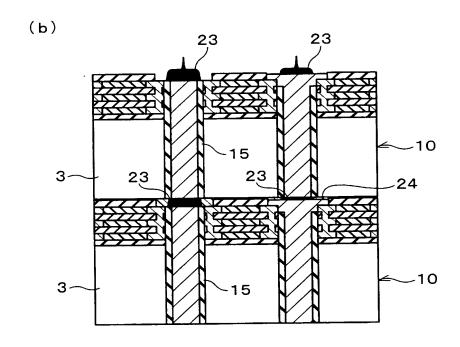

## [0101]

[実施の形態2]

本発明の他の実施の形態について図10ないし図20に基いて説明すれば、以下の通りである。なお、説明の便宜上、前記の実施の形態1の図面に示した部材と同一の機能を有する部材については、同一の符号を付し、その説明を省略する。

## [0102]

本実施の形態では、電極パッド2の領域外にさらに貫通電極1を設ける場合に ついて説明する。

#### $[0\ 1\ 0\ 3\ ]$

例えば、積層型半導体装置が多段になる程、各半導体装置10…での熱の発生も多くなることから、各半導体装置10…で発生する熱を積層型半導体装置の下側に逃すことが好ましい。したがって、その場合等においては、電気的な動作をせず、下層又は上層の半導体装置10の橋渡し的な役目のみを行うスルー用貫通電極12が必要になる。

## [0104]

また、積層型半導体装置における中間層の各半導体装置 1 0 …同士で、電気的な接続がさらに必要となる場合がある。

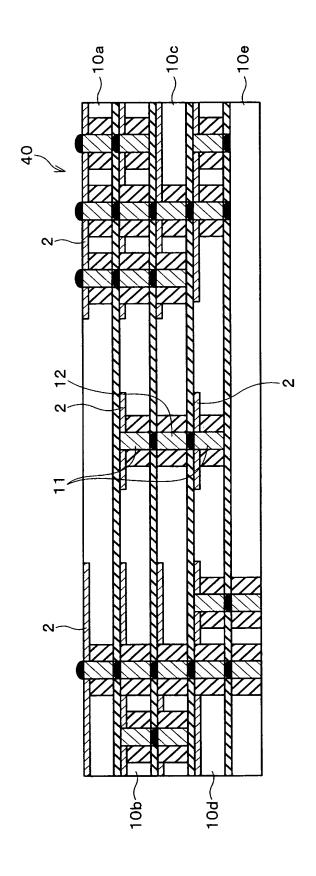

## [0105]

そこで、本実施の形態の積層型半導体装置 4 0 では、図 1 0 及び図 1 1 (a) ~ (e) に示すように、第 2 半導体装置 1 0 b、第 3 半導体装置 1 0 c、第 4 半導体装置 1 0 d、及び第 5 半導体装置 1 0 e を接続するスルー用貫通電極 1 2 を

、電極パッド2・2の間に形成している。また、図12に示すように、既存の電極パッド2・2(同図において左右に設けられているもの)の間に、第2半導体装置10b及び第4半導体装置10dには接続用貫通電極11を形成し、第3半導体装置10cにはスルー用貫通電極12を形成することが可能である。なお、この場合、第2半導体装置10b及び第4半導体装置10dにおける接続用貫通電極11の形成に際しては、新たに電極パッド2を形成する必要がある。

# [0106]

すなわち、貫通電極1を新たに形成する場合に、電極パッド2が存在する領域 に既に貫通電極1が多く形成するときには、当該電極パッド2の領域には最早貫 通電極1を設けることができない場合がある。このような場合に、本実施の形態 では、電極パッド2の領域ではない部分にも貫通電極1を形成する方法を提供す るものである。

## [0107]

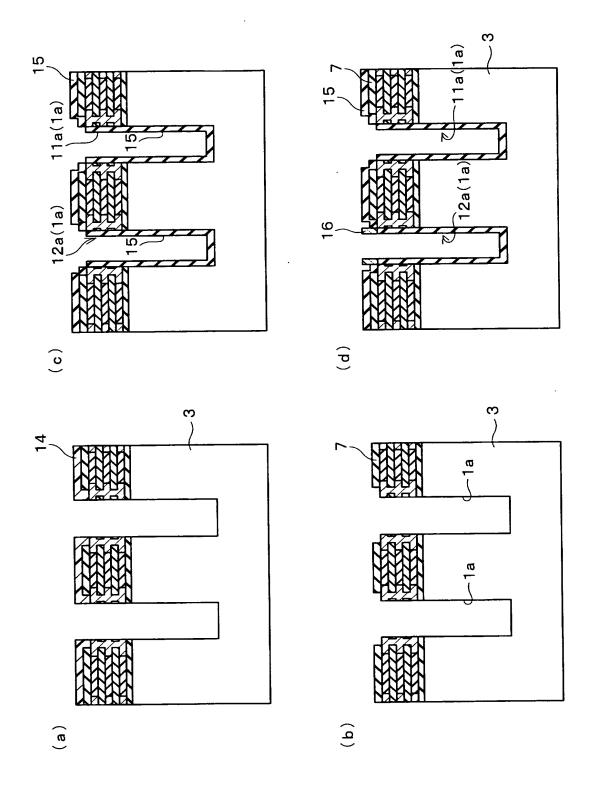

上記構成の半導体装置10における電極パッド2・2の間に、スルー用貫通電極12を形成するに際して、電極パッド2に貫通電極を設けると同時に電極パッド2・2の間にスルー用貫通電極12又は接続用貫通電極11を形成する方法について、図13~図19に基いて説明する。なお、本工程は、前記実施の形態1の製造工程と略同様の工程で進んでいくので、詳細説明は省略する。

#### [0108]

本実施の形態においても、図13 (a) に示すように、既存の半導体装置10 の周辺部において、表面のパッシベーション膜7から露出する電極パッド2が2 箇所に設けられている。すなわち、同図(a) は、実施の形態1の図4(a) と同じである。

#### [0109]

本実施の形態では、これら電極パッド2・2の間にも貫通電極1を形成する。 すなわち、この電極パッド2・2の間の領域の下は層間絶縁膜6であることから 、配線パターン5…等が無く、スルー用貫通電極貫通孔を開けるスペースとして 確保するができる。

## [0110]

まず、ウエハ表面全体にレジスト14の塗布を行い、次いで、図13 (b) に示すように、貫通パターン作成のため、縮小投影型露光機を使用し、電極パッド2の領域内、及び電極パッド2・2の間を、例えば10μm角の貫通孔用のパターンを開口し、電極パッド2、及び電極パッド2・2の間を露出した状態にする。

# [0111]

次いで、図13(c)(d)、及び図14(a)(b)(c)(d)に示すように、実施の形態1と同様のエッチング方式にて、配線パターン5…及び層間絶縁膜6…のエッチングを行う。このとき、金属エッチング時のプロセスでは層間絶縁膜6のエッチングレートつまりエッチングする速度は極めて遅いので、電極パッド2・2の間のエッチングが電極パッド2領域のエッチングに比べて遅くなる。

# [0112]

次いで、図15 (a) に示すように、エッチングの最終ステップで残っている 層間絶縁膜6 の絶縁残膜をエッチングする。このとき、シリコン (Si) 基板 3 も 1 ミクロン程度のオーバーエッチング量があるものの、その後に、図15 (b) に示すように、シリコン (Si) 基板 3 を 5 0  $\mu$  m から 7 0  $\mu$  m エッチングを するので、問題になる数値では無い。

#### [0113]

次いで、図15 (b) (c) (d) ~図18 (a) に示すように、前記実施の 形態1における図6 (b) (c) (d) ~図9 (a) と同様のプロセスを行う。

#### $[0\ 1\ 1\ 4\ ]$

次いで、図18(b)に示すように、このように形成した半導体装置10・10を導電性シート24にて接着することにより、積層型半導体装置40が完成する。

# [0115]

なお、上記の説明では、図16(a)(b)(c)(d)~図17(a)(b)に示すように、右側の接続用貫通電極11の形成において、再配線パターン5cを形成した後、バンプ23を形成していた。しかしながら、必ずしもこれに限

らず、例えば、図19(a)(b)(c)(d) $\sim$ 図20に示すように、再配線 パターン5cを形成することなく、バンプ23を形成することも可能である。これにより、再配線を無くすことができる。

## [0116]

このように、本実施の形態の積層型半導体装置 4 0 では、電極パッド 2 の領域外にさらに貫通電極 1 が設けられているので、電極パッド 2 の領域内に貫通電極 1 を形成し、さらに、電極パッド 2 の領域外にもさらに貫通電極 1 を形成することによって、多層の積層型半導体装置 4 0 にも対応することが可能となる。

## [0117]

また、本実施の形態の積層型半導体装置 4 0 では、各半導体装置 1 0 の貫通電 極 1 同士がバンプ 2 3 を介して接続されることにより、各半導体装置 1 0 が積層 されているので、積層工程を容易に行うことができる。

## [0118]

また、本実施の形態の積層型半導体装置 4 0 の製造方法は、半導体装置製造工程において、電極パッド 2 の領域外にもさらに貫通電極 1 を形成する工程を含む。したがって、電極パッド 2 の領域内に貫通電極 1 を形成し、さらに、電極パッド 2 の領域外にもさらに貫通電極 1 を形成することによって、多層の積層型半導体装置 4 0 にも対応できる積層型半導体装置 4 0 を容易に製造することができる

#### [0119]

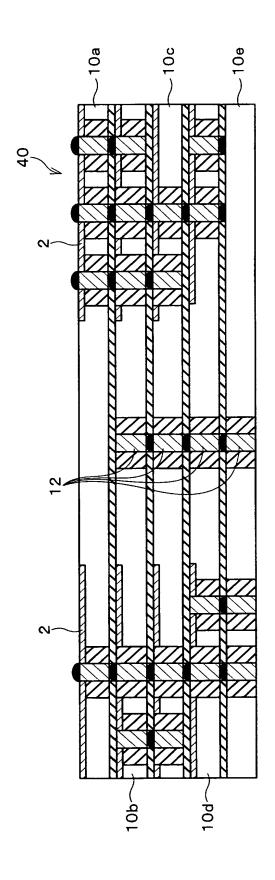

## [実施の形態3]

本発明の他の実施の形態について図21及び図22に基いて説明すれば、以下の通りである。なお、説明の便宜上、前記の実施の形態1及び実施の形態2の図面に示した部材と同一の機能を有する部材については、同一の符号を付し、その説明を省略する。

#### [0120]

既存の半導体装置10において、外部取り出し用の電極パッド2が半導体装置10の周辺に並んでいるタイプでは、電極パッド2が一般に大き過ぎ、スペース的に余裕がなくなり、スルー用貫通電極12…を形成するためのスペースを確保

することが厳しくなる。

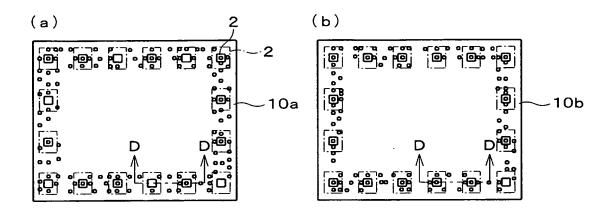

## [0121]

そこで、本実施の形態の積層型半導体装置50では、図21及び図22(a) (b) (c) (d) (e) に示すように、各半導体装置10…における配線パターン5…における電極パッド2の領域を縮小するようにマスク変更を行い、電極パッド2の仕上がりサイズを縮小する。

## [0122]

すなわち、既存の半導体装置 10 における電極パッド 20 の大きさは、図 22 (a) (b) (c) (d) (e) において一点鎖線で示すように、 $70\mu$  m角である。本実施の形態では、この電極パッド 20 の大きさを例えば仕上がりサイズ 15  $\mu$  m角に変更している。

## [0123]

これによって、余裕のできたスペースに、スルー用貫通電極12のスルー用貫通電極貫通孔12aのパターンとともに、通常の貫通孔1aも前記実施の形態一及び実施の形態2と同様に、レジスト14を塗布した後、縮小投影型露光機を使用して作成する。

#### [0124]

このとき、スルー用貫通電極貫通孔12aを形成するためのパターンの下は全て層間絶縁膜6となっているので、実施の形態1及び実施の形態2と同様のエッチング方式にエッチングを行う。したがって、金属エッチング時のプロセスでは、前記実施の形態1にて説明したように、層間絶縁膜6のエッチングレートは極めて遅くなる。

## [0125]

また、図は省略するが、エッチングの最終ステップで残っている層間膜 130 絶縁残膜をエッチングする際、シリコン(Si)基板 361 ミクロン程度のオーバーエッチング量があるものの、その後にシリコン(Si)基板 3650  $\mu$  mか 670  $\mu$  mエッチングをするので、問題になる数値では無い。

## [0126]

エッチング後の工程は、前記実施の形態1及び実施の形態2と同じ工程である

0

## [0127]

このように、本実施の形態の積層型半導体装置50では、半導体装置製造工程において、貫通孔1aを形成する工程の前に、素子領域4から導かれる電極パッド2を形成する工程を含むとともに、電極パッド2を形成する工程では、電極パッド2の領域をマスク変更により省スペース化して形成する一方、省スペース化による電極パッド空き領域に貫通電極1を形成する工程をさらに含む。

## [0128]

したがって、従来では、大きな電極パッド2が存在したが、その電極パッド2を小さく形成することによって、従来電極パッド2があるはずの箇所に生まれたスペースにさらに貫通電極1を形成することができる。

## [0129]

# [実施の形態4]

本発明の他の実施の形態について図23ないし図29に基いて説明すれば、以下の通りである。なお、説明の便宜上、前記の実施の形態1ないし実施の形態3の図面に示した部材と同一の機能を有する部材については、同一の符号を付し、その説明を省略する。

#### [0130]

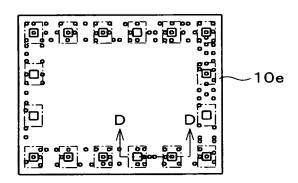

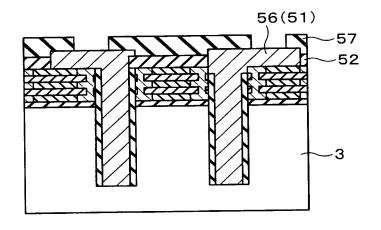

複数の半導体装置10を用いて積層型半導体装置を形成する場合に、上下の半導体装置10・10における貫通電極1・1の貫通孔1a・1a同士がパターンレイアウト上、合わないときが多々発生する。その解決策として、本実施の形態では、ウエハ裏面又はウエハ表面に再配線を行い、問題を解決している。

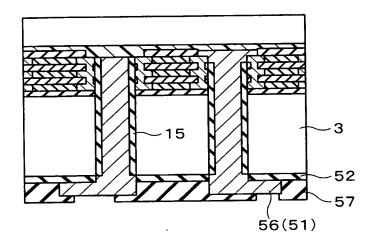

# [0131]

すなわち、本実施の形態の積層型半導体装置50では、図23に示す上側の半導体装置10における貫通電極1の位置と、同図に示す下側の半導体装置10における貫通電極1の位置とが一致していない。しかし、この場合、図23に示す上側の半導体装置10における裏面に再配線51を形成することにより、上側の半導体装置10における貫通電極1と、下側の半導体装置10における貫通電極1とを電気的に接続させている。

# [0132]

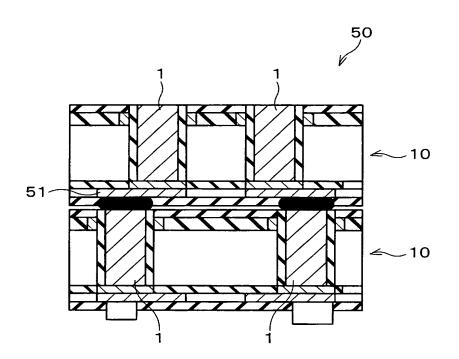

上記の再配線51の形成方法を図24及び図25に基いて説明する。

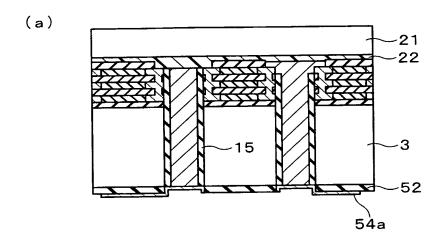

# [0133]

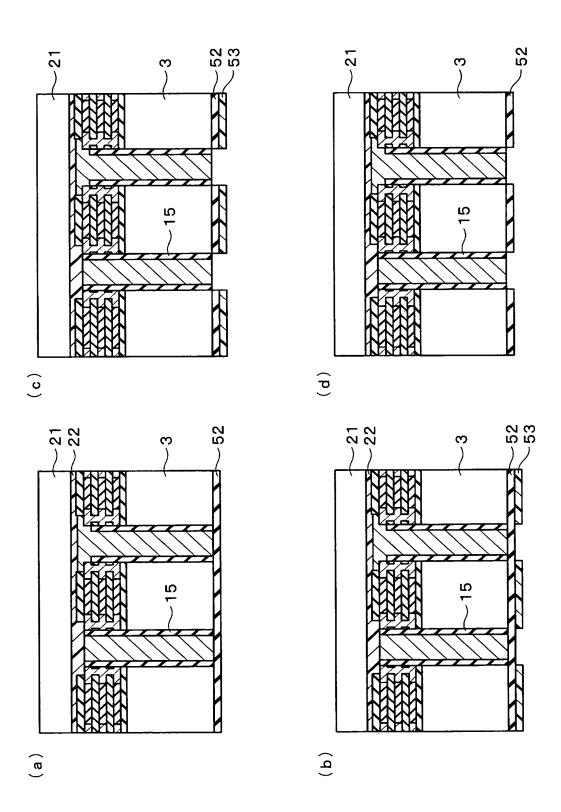

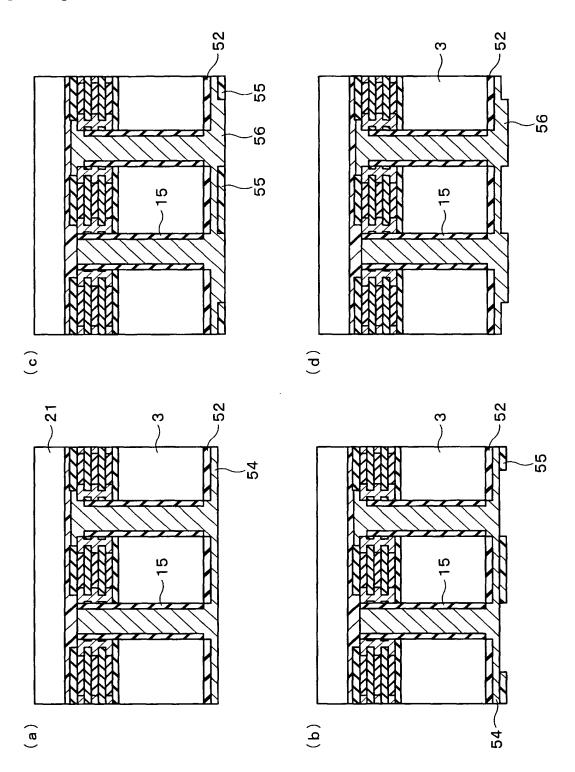

まず、図24(a)に示すように、前記実施の形態1及び実施の形態2におけるウエハ裏面研磨完了後、補強板21を取り除く前の状態において(図8(c)参)、ウエハ裏面側に絶縁膜52のデポジットを行い、次いで、図24(b)に示すように、レジスト53を塗布した後、図24(c)に示すように、縮小投影型露光機を使用して上記絶縁膜52をエッチングする。

# [0134]

次いで、図24 (d) に示すように、レジスト53を剥離した後、図25 (a) に示すように、バリアメタル及び導電物54を順番につけ、もう一度、レジスト54を塗布する。この理由は、次工程にて電解メッキを行うが、図25 (b) に示すように、付けたくない所に予めレジスト55にてカバーしておくためである。なお、上記バリアメタルとは、アルミニウム (A1)・銅 (Cu)・タングステン (W) 等の金属配線、或いはタングステン (W) プラグを用いた埋め込みコンタクトやビアホール、さらにデュアルダマシンプロセスによる銅 (Cu)の埋め込みビアホール等と、各種絶縁膜、シリコン (Si) 等の半導体基板、多結晶シリコン層、シリサイド層、さらに他の配線層との接続部において、界面に設けられた障壁膜をいう。バリア膜には、接続部における合金反応やシリコン (Si)の金属配線への拡散を抑える目的があり、チタンナイトライド・チタンタングステン・タングステンナイトライド・タンタルナイチライド等が使われることが多い。

## [0135]

また、上記導電物 5 4 は、例えば、アルミニウム (A 1) ・銅 (C u) ・タングステン (W) 等の電気を流すものである。

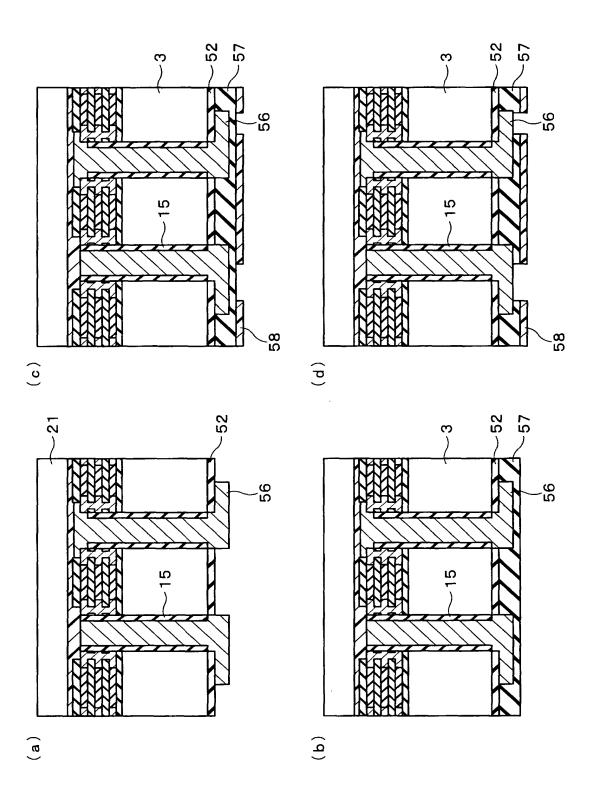

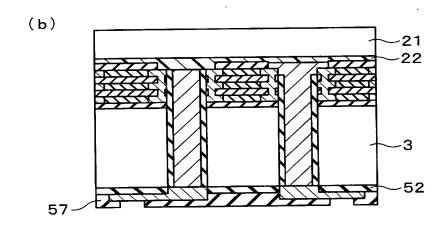

#### $[0\ 1\ 3\ 6]$

次いで、図25 (c) (d) に示すように、導体56を電解メッキ後、レジスト55の剥離を行い、さらに、図26 (a) に示すように、薬品にて不必要なメッキ部分を取り省き、図26 (b) に示すように、その上から保護膜57をつけ

る。

# [0137]

次いで、図26 (c) に示すように、レジスト58をパターニングし、図26 (d) に示すように、エッチングにて開口する。最後に、図27に示すように、レジスト58の剥離を行うことにより完了する。

# [0138]

なお、上記の例では、半導体装置10の裏面に再配線51を形成したが、図28に示すように、ウエハ裏面研磨行程の前に上記半導体装置10の表面に再配線51を施すことも可能である。

## [0139]

また、本実施の形態では、導体56の形成に際して、電解メッキにて行ったが、必ずしもこれに限らず、例えば、無電解メッキにて行うことが可能である。この無電解メッキは、電解メッキに際して電極も外部電源も不要なプロセスである。この無電界メッキ工程においては、導体は触媒の役目をし、メッキに変化する。

# [0140]

この場合は、前記図24(a)(b)(c)(d)に示すように、ウエハ裏面の研磨完了後、補強板21を取り除く前の状態において、ウエハ裏面側に絶縁膜52の堆積を行い、レジスト53を塗布した後、縮小投影型露光機を使用して絶縁膜52をエッチングする。

## $[0 \ 1 \ 4 \ 1]$

次いで、図29(a)に示すように、バリアメタル54aをスパッタし、図示しないレジストを塗布した後エッチングを行い、無電解メッキをしたい部分のみ残す。

## [0142]

その後は、前記図26 (b) (c) (d)、及び図27に示す工程と同様にして、最終的に、図29 (b) に示すように、保護膜57を施して完了する。

## [0143]

# 【発明の効果】

本発明の積層型半導体装置は、以上のように、素子領域から導かれる電極パッドの領域内に半導体チップの表裏間を貫通する貫通電極が複数個接続されてなる 半導体装置が複数積層されているものである。

# [0144]

それゆえ、電極パッドの領域を貫通電極の形成スペースに使用できる。この結果、半導体チップの周辺部を広く形成する必要がないので、半導体チップの周辺部だけではスペースを確保できなくなるのを緩和させることができるとともに、 積層型半導体装置の小型化を図ることができる。また、多段積層も容易に実現できるようになる。

## [0145]

したがって、多数の貫通電極を設けることに伴う、装置の大型化防止及び多段 積層の困難化解消を図り得る積層型半導体装置を提供することができるという効 果を奏する。

## [0146]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記各電極パッドは、素子領域を取り囲むように各半導体チップの周辺に設けら れているものである。

#### [0147]

それゆえ、貫通電極を形成する際に素子領域が邪魔になるということがないという効果を奏する。

## [0148]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記貫通電極のうち少なくとも1種類は、前記電極パッドと電気的に接続される 接続用貫通電極であるものである。

#### [0149]

それゆえ、一般的な素子領域に接続される接続用貫通電極を形成することがで きるという効果を奏する。

## [0150]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、

前記貫通電極のうち少なくとも1種類は、前記電極パッドとは電気的に接続されないスルー用貫通電極であるものである。

# [0151]

それゆえ、貫通電極として、素子領域に接続されないで単に半導体装置をスルーするためだけのスルー用貫通電極が設けられることになる。この結果、半導体装置に発生する熱をスルー用貫通電極を介して外部に逃したり、上層の半導体装置の接続用貫通電極に連結することにより、下層の半導体装置側に導くことができるという効果を奏する。

## [0152]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、前記電極パッドの領域外にさらに貫通電極が設けられているものである。

## [0153]

それゆえ、電極パッドの領域内に貫通電極を形成し、さらに、電極パッドの領域外にもさらに貫通電極を形成することによって、多層の積層型半導体装置にも対応することが可能となるという効果を奏する。

#### [0154]

また、本発明の積層型半導体装置は、上記記載の積層型半導体装置において、 前記各半導体装置の貫通電極同士がバンプを介して接続されることにより、各半 導体装置が積層されているものである。

## [0155]

それゆえ、積層工程を容易に行うことができるという効果を奏する。

#### [0156]

また、本発明の積層型半導体装置の製造方法は、以上のように、半導体装置を 形成する半導体装置製造工程と、上記半導体装置を複数積層する半導体装置積層 工程とを含む一方、上記半導体装置製造工程は、素子領域から導かれた電極パッドの領域内に所定形状の開口部を有するマスクを用いて、上記電極パッドを貫い て半導体チップに所定の深さを有する溝部を形成する工程と、上記溝部の内壁に 絶縁膜を形成する工程と、上記溝部に導電材料を充填する工程と、上記半導体チップの裏面の一部を除去して上記導電材料を露出させることにより、半導体チッ プの表裏を貫通する上記導電材料からなる貫通電極を形成する工程とをこの順に 含む方法である。

# [0157]

それゆえ、この工程にて積層型半導体装置を製造することにより、例えば、既存の電極パッドが形成された半導体装置にて積層型半導体装置の製造する場合に おいて、容易に、電極パッドの領域内に貫通電極を形成することができる。

## [0158]

したがって、多数の貫通電極を設けることに伴う、装置の大型化防止及び多段 積層の困難化解消を図り得る積層型半導体装置の製造方法を提供することができ るという効果を奏する。

## [0159]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置の製造方法において、前記半導体装置製造工程における溝部の内壁に絶縁膜を形成する工程と前記溝部に導電材料を充填する工程との間に、上記溝部の内壁に形成した絶縁膜のうち、電極パッドと同層部分を除去する工程を含む方法である。

#### [0160]

それゆえ、スルー用貫通電極を容易に形成することができるという効果を奏する。

## [0161]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置 の製造方法において、前記半導体装置製造工程において、前記電極パッドの領域 外にもさらに貫通電極を形成する工程を含む方法である。

## [0162]

それゆえ、電極パッドの領域内に貫通電極1を形成し、さらに、電極パッドの 領域外にもさらに貫通電極を形成することによって、多層の積層型半導体装置に も対応できる積層型半導体装置を容易に製造することができるという効果を奏す る。

## [0163]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置

の製造方法において、前記半導体装置製造工程において、前記溝部を形成する工程の前に、素子領域から導かれる電極パッドを形成する工程を含むとともに、上記電極パッドを形成する工程では、電極パッドの領域をマスク変更により省スペース化して形成する一方、上記省スペース化による電極パッド空き領域に貫通電極を形成する工程をさらに含む方法である。

## [0164]

それゆえ、従来では、大きな電極パッドが存在したが、その電極パッドを小さく形成することによって、従来電極パッドがあるはずの箇所に生まれたスペースにさらに貫通電極を形成することができるという効果を奏する。

## [0165]

また、本発明の積層型半導体装置の製造方法は、上記記載の積層型半導体装置の製造方法において、前記半導体装置製造工程における電極パッドを貫いて半導体チップに所定の深さを有する溝部を形成する工程において、上記溝部は電極パッドの領域内に複数形成される方法である。

#### [0166]

それゆえ、一つの電極パッドの領域内に、接続用貫通電極とスルー用貫通電極 とを複数個形成することができるという効果を奏する。

### 【図面の簡単な説明】

## 【図1】

本発明における積層型半導体装置の実施の一形態を示すものであり、図2 (a) ~ (e) のA-A線断面図である。

#### 【図2】

(a)~(e)は積層型半導体装置の各半導体装置の構成を示す平面図である

#### 【図3】

(a) は本実施の形態で使用する半導体装置の構成を示す平面図であり、(b) は一部を破断して示す(a)のB-B線拡大断面図である。

## 【図4】

(a)~(d)は、半導体装置の貫通電極の製造工程を示す断面図である。

# 【図5】

(a) ~ (d) は、半導体装置の貫通電極における図4の続きの製造工程を示す断面図である。

# 【図6】

(a) ~ (d) は、半導体装置の貫通電極における図5の続きの製造工程を示す断面図である。

## 【図7】

(a) ~ (d) は、半導体装置の貫通電極における図6の続きの製造工程を示す断面図である。

## 【図8】

(a) ~ (d) は、半導体装置の貫通電極における図7の続きの製造工程を示す断面図である。

## 【図9】

(a) は、半導体装置の貫通電極における図8の続きの製造工程を示すものであり、貫通電極に金バンプを形成した半導体装置を示す断面図である。また、(b) は、(a) の半導体装置を積層することにより完成した積層型半導体装置を示す断面図である。

### 【図10】

本発明における積層型半導体装置の他の実施の形態を示すものであり、図11 (a)~(e)のC-C線断面図である。

#### 【図11】

$(a) \sim (e)$  は、上記積層型半導体装置における各半導体装置の構成を示す 平面図である。

#### 【図12】

上記積層型半導体装置の他の形態を示す断面図である。

#### 【図13】

$(a) \sim (d)$  は、図10に示す積層型半導体装置の製造工程を示す断面図である。

#### 【図14】

$(a) \sim (d)$  は、図13の続きの製造工程を示す断面図である。

### 【図15】

$(a) \sim (d)$  は、図14の続きの製造工程を示す断面図である。

### 【図16】

(a) ~ (d) は、図15の続きの製造工程を示す断面図である。

#### 【図17】

$(a) \sim (d)$  は、図16の続きの製造工程を示す断面図である。

### 【図18】

- (a) は、半導体装置の貫通電極における図17の続きの製造工程を示すものであり、貫通電極に金バンプを形成した半導体装置を示す断面図である。また、

- (b) は、(a) の半導体装置を積層することにより完成した積層型半導体装置を示す断面図である。

### 【図19】

$(a) \sim (d)$  は、図16(b)の続きを示すものであり、再配線パターンを行うことなく、バンプを形成する場合の製造工程を示す断面図である。

#### 【図20】

再配線パターンを行うことなく、バンプを形成して完成した半導体装置を示す 断面図である。

#### 【図21】

本発明における積層型半導体装置のさらに他の実施の形態を示すものであり、 図 2 2 (a)  $\sim$  (e) のD-D線断面図である。

#### 【図22】

(a)~(e)は、上記積層型半導体装置における各半導体装置の構成を示す 平面図である。

#### 【図23】

本発明における積層型半導体装置のさらに他の実施の形態を示すものであり、 上記積層型半導体装置において、上下の半導体装置における貫通電極の位置が揃っていない場合の該貫通電極の接続状態を示す断面図である。

#### 【図24】

(a) ~ (d) は、図23に示す積層型半導体装置の製造工程を示す断面図である。

# 【図25】

(a) ~ (d) は、図24の続きの製造工程を示す断面図である。

# 【図26】

$(a) \sim (d)$  は、図25の続きの製造工程を示す断面図である。

# 【図27】

上記の製造工程により完成した、ウエハ裏面に導体を形成した半導体装置を示す断面図である。

# 【図28】

ウエハ表面に導体を形成した半導体装置を示す断面図である。

# 【図29】

(a) (b) は、無電解メッキにより導体を形成する場合の製造工程を示す断面図である。

### 【図30】

従来の半導体装置を示す断面図である。

# 【図31】

従来の他の半導体装置を示す断面図である。

# 【図32】

従来の積層型半導体装置を示す断面図である。

# 【符号の説明】

- 1 貫通電極

- 1 a 貫通孔(溝部)

- 2 電極パッド

- 4 素子領域

- 3 シリコン(Si) 基板

- 5 配線パターン

- 7 パッシベーション膜

- 8 半導体チップ

- 10 半導体装置

- 11 接続用貫通電極(貫通電極)

- 11a 接続用貫通電極貫通孔

- 12 スルー用貫通電極(貫通電極)

- 12a スルー用貫通電極貫通孔

- 14 レジスト (マスク)

- 15 側壁絶縁膜(絶縁膜)

- 20 導体(導電材料)

- 23 バンプ

- 30 積層型半導体装置

- 40 積層型半導体装置

- 50 積層型半導体装置

- 5 1 再配線

# 【書類名】 図面

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

# 【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

်ပ

(**p**)

【図20】

【図21】

# 【図22】

(e)

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

# 【図31】

【図32】

【書類名】 要約書

【要約】

【課題】 多数の貫通電極を設けることに伴う、装置の大型化防止及び多段積層の困難化解消を図り得る積層型半導体装置を提供する。

【解決手段】 積層型半導体装置30は、素子領域から導かれる電極パッド2の領域内に半導体チップの表裏間を貫通する貫通電極1が複数個接続されてなる半導体装置10a~10eが複数積層されている。

【選択図】 図1

特願2002-313528

出願人履歴情報

識別番号

[000005049]

1. 変更年月日

1990年 8月29日

[変更理由]

新規登録

住 所

大阪府大阪市阿倍野区長池町22番22号

氏 名 シャープ株式会社

•